RX的规格书N5 N5-Datasheet-release-v00-20200303.pdf

版权说明:本文档由用户提供并上传,仅供个人学习用途,若内容存在侵权,请联系我们删除。

N5_Datasheet_release_v00_20200303.pdf

(1.22 MB, 售价: 5 E币)

N5_Datasheet_release_v00_20200303.pdf

(1.22 MB, 售价: 5 E币)

高达8M 15P的信号,暗示N5在解析度和带宽上有较高的性能。 3. **通用性**: 作为一款通用接收器,N5可能设计有广泛的兼容性,能够适应多种不同的应用场景。 4. **质量保证**: 产品设计注重高质量信号接收,可能具备低噪声、高信噪比等特性,以确保数据的准确传输。 5. **安全性警告**: 明确指出产品不适用于生命支持应用,这是为了遵守行业规定和安全标准。 文档还提醒用户,尽管提供了信息,但Nextchip不对文档内容导致的任何损害负责,而且提供的信息“AS IS”,即不提供任何明示或暗示的保证。此外,Nextchip不承担因使用这些信息而产生的间接损害的责任。 Nextchip公司的联系信息也在文档中给出,包括网址、电子邮件地址和电话号码,方便用户获取更多产品支持和服务。 总体来说,N5是一款面向特定领域的高性能接收器,适用于需要高质量信号处理的系统。其设计考虑了多种使用环境,但明确排除了医疗领域的应用。用户在使用N5时,应遵循文档的指导,确保正确理解和应用产品的各项特性。

TABLE OF CONTENTS

Revision History....................................................................................................................................................... 2

Contents of Tables ................................................................................................................................................... 6

Contents of Figures ................................................................................................................................................. 7

Chapter 1 PIN INFORMATION.............................................................................................................................. 8

1.1 PIN ASSIGNMENTS ................................................................................................................................ 8

1.2 PIN DESCRIPTION.................................................................................................................................. 9

Chapter 2 UNIVERSAL RX(1M to 8M15P) ......................................................................................................... 10

2.1 FUNCTIONAL OVERVIEW .................................................................................................................... 10

2.1 ANALOG FRONT END (CLAMP, ANTI-ALIASING FILTER, EQ FILTER) ...............................................11

2.2 GENLOCK (ROBUST SYNC DETECTION, ROBUST NO-VIDEO DETECTION)...................................11

2.3 YCS (Y/C SEPARATOR) .........................................................................................................................11

2.4 LUMA PROCESSING..............................................................................................................................11

2.5 CHROMA PROCESSING........................................................................................................................11

2.6 DATA OUTPUT ORDER & DIRECTION CONTROL .............................................................................. 12

2.7 OUTPUT FORMAT................................................................................................................................. 13

2.7.1 ITU-R BT.656/BT.1120 FORMAT ................................................................................................. 13

2.7.2 ITU-R BT.601 FORMAT ............................................................................................................... 13

2.7.3 VIDEO OUTPUT TIMING INFORMATION .................................................................................. 14

2.8 OUTPUT MODE..................................................................................................................................... 16

2.8.1 SINGLE OUTPUT MODE ............................................................................................................ 16

2.8.2 2-MULTIPLEX OUTPUT MODE .................................................................................................. 17

2.9 297MHz INTERFACE AND MULTI STANDARD OUTPUT MODE ......................................................... 18

2.10 Video Frame Control .............................................................................................................................. 18

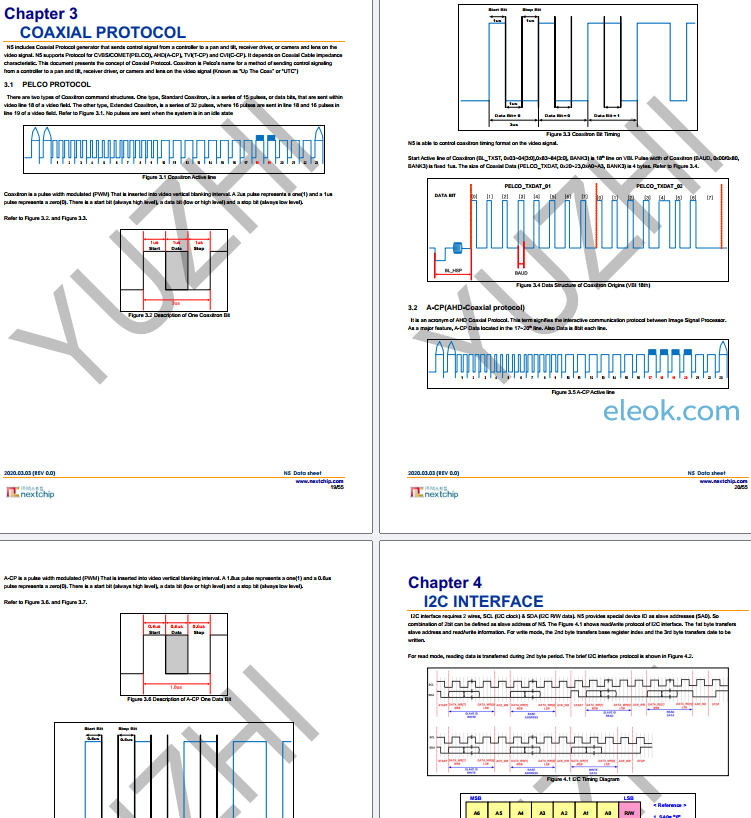

Chapter 3 COAXIAL PROTOCOL ...................................................................................................................... 19

3.1 PELCO PROTOCOL .............................................................................................................................. 19

3.2 A-CP(AHD-Coaxial protocol).................................................................................................................. 20

Chapter 4 I2C INTERFACE................................................................................................................................. 22

Chapter 5 REGISTER DESCRIPTION................................................................................................................ 23

5.1 REGISTER ADDRESS........................................................................................................................... 23

5.1.1 BANK0 Register(0x00~0x3D) : VIDEO........................................................................................ 23

5.1.2 BANK0 Register(0x40~0x7A) : VIDEO........................................................................................ 24

5.1.3 BANK0 Register(0x80~0xA1) : VIDEO_ENABLE & Delay .......................................................... 25

5.1.4 BANK0 Register(0xA8~0xF4) : STATUS ..................................................................................... 26

5.1.5 BANK1 Register(0x80~0x9F) : IP Power Down........................................................................... 27

5.1.6 BANK1 Register(0xB0~0xBF) : MPP........................................................................................... 27

5.1.7 BANK1 Register(0xC0~0xCF) : OUTPUT PORT......................................................................... 27

5.1.8 BANK3 Register(0x00~0x7F / 0x80~0xFF ) : COAXIAL CH1~2.................................................. 28

5.1.9 BANK3 Register(0x00~0x1F / 0x80~0x9F ) : COAXIAL CH1~2.................................................. 28

5.1.10 BANK3 Register(0x20~0x5F / 0xA0~0xDF ) : COAXIAL CH1~2................................................. 29

5.1.11 BANK3 Register(0x60~0x79 / 0xE0~0xF9 ) : COAXIAL CH1~2.................................................. 30

5.2 Register Description ............................................................................................................................... 31

5.2.1 VIDEO Registers ......................................................................................................................... 31

5.2.2 State Registers ............................................................................................................................ 40

5.2.3 Power Down Registers ................................................................................................................ 42

5.2.4 MPP Control Registers ................................................................................................................ 43

5.2.5 Video Output Control Registers ................................................................................................... 44

5.2.6 COAXIAL Registers ..................................................................................................................... 46

Chapter 6 ELECTRICAL CHARACTERISTICS.................................................................................................. 52

6.1 ABSOLUTE MAXIMUM RATINGS ......................................................................................................... 52

6.2 RECOMMENDED OPERATING CONDITION........................................................................................ 52

6.3 DC CHARACTERISTICS ....................................................................................................................... 52

6.4 AC CHARACTERISTICS........................................................................................................................ 53

6.5 RECOMMENDED POWER-ON/OFF, PLL SEQUENCE ........................................................................ 54

Chapter 7 PACKAGE INFORMATION ................................................................................................................ 55

Contents of Tables

Table 1.1 N5 PIN Description........................................................................... 9

Table 2.1 Data Output Pin Order Control ............................................................. 12

Table 2.2 Output Clock and Data Direction Control .............................................. 12

Table 2.3 Each Port 1-Channel Normal mode or X-Format Setting ................................................. 16

Table 2.4 Each Port 2-Channel Normal mode or X-Format Setting ........................................... 17

CONTENTS OF FIGURES

Figure 1.1 N5 Pin Assignments............................................................................. 8

Figure 2.1 Universal RX Video Processing of N5 ........................................................... 10

Figure 2.2 Region of active is constant................................................................... 13

Figure 2.3 BT.601 Interface............................................................................... 13

Figure 2.4 AHD720P@30P/25P, 60P/50P Horizontal Timing Diagram ............................................. 14

Figure 2.5 AHD720P@30P/25P, 60P/50P Vertical Timing Diagram ............................................... 14

Figure 2.6 AHD1080P@30P/25P Horizontal Timing Diagram ..................................................... 15

Figure 2.7 AHD1080P@30P/25P Vertical Timing Diagram.........................................................15

Figure 2.8 Block Diagram of Single-Channel Output .........................................................16

Figure 2.9 Block Diagram of of Multiplexed 2-Channels Output ............................................... 17

Figure 3.1 Coaxitron Active line .......................................................................... 19

Figure 3.2 Description of One Coaxitron Bit .................................................................19

Figure 3.3 Coaxitron Bit Timing ...........................................................................20

Figure 3.4 Data Structure of Coaxitron Origins (VBI 18th)...................................................20

Figure 3.5 A-CP Active line ................................................................................20

Figure 3.6 Description of A-CP One Data Bit.................................................................21

Figure 3.7 Data A-CP Bit Timing............................................................................. 21

Figure 3.8 Data Structure of Coaxitron Origins (VBI 17th)...................................................21

Figure 4.1 I2C Timing Diagram................................................................................ 22

Figure 4.2 I2C Slave Address Configuration....................................................................22

Figure 6.1 SCL and SDA Timing Diagram........................................................................53

Figure 6.2 Recommended Power-on/off Sequence................................................................54

Figure 7.1 N5 54Pin Package Information ....................................................................55

【必读】版权免责声明

1、本主题所有言论和内容纯属会员个人意见,与本论坛立场无关。2、本站对所发内容真实性、客观性、可用性不做任何保证也不负任何责任,网友之间仅出于学习目的进行交流。3、对提供的数字内容不拥有任何权利,其版权归原著者拥有。请勿将该数字内容进行商业交易、转载等行为,该内容只为学习所提供,使用后发生的一切问题与本站无关。 4、本网站不保证本站提供的下载资源的准确性、安全性和完整性;同时本网站也不承担用户因使用这些下载资源对自己和他人造成任何形式的损失或伤害。 5、本网站所有软件和资料均为网友推荐收集整理而来,仅供学习用途使用,请务必下载后两小时内删除,禁止商用。6、如有侵犯你版权的,请及时联系我们(电子邮箱1370723259@qq.com)指出,本站将立即改正。

|