|

文档下载: 版权说明:本文档由用户提供并上传,仅供个人学习用途,若内容存在侵权,请联系我们删除。

μPD720201μPD720202 Users Manual Hardware.pdf

(3 MB, 售价: 3 E币)

μPD720201μPD720202 Users Manual Hardware.pdf

(3 MB, 售价: 3 E币)

Renesas μPD720201/μPD720202 User’s Manual: Hardware Rev.3.00 May 2012 USB3.0 HOST CONTROLLER

Overview

The μPD720201 and μPD720202 are Renesas’ third generation Universal Serial Bus 3.0 host controllers,which comply with Universal Serial Bus 3.0 Specification, and Intel’s eXtensible Host Controller Interface(xHCI). These devices reduce power consumption and offer a smaller package footprint making them ideal for designers who wish to add the USB3.0 interface to mobile computing devices such as laptops and notebook computers.

The μPD720201 supports up to four USB3.0 SuperSpeed ports and the μPD720202 supports up to two USB3.0 SuperSpeed ports. The μPD720201 and μPD720202 use a PCI Express® Gen 2 system interface bus allowing system designers to easily add up to four (μPD720201) or two (μPD720202) USB3.0 SuperSpeed ports to systems containing the PCI Express bus interface. When connected to USB 3.0-compliant peripherals, the μPD720201 and μPD720202 can transfer information at clock speeds of up to 5 Gbps. The μPD720201 and μPD720202 and USB 3.0 standard are fully compliant and backward compatible with the previous USB2.0 standard. The new USB 3.0 standard supports data transfer speeds of up to ten times faster than those of the previous-generation USB2.0 standard, enabling quick and efficient transfers of large amounts of information.

PREFACE

Readers This manual is intended for engineers who need to be familiar with the capabilityof the μPD720201/μPD720202 in order to develop application systems based on

it.Purpose The purpose of this manual is to help users understand the hardware capabilities(listed below) of the μPD720201/μPD720202.

Configuration This manual consists of the following chapters:

• Overview

• Pin function

• Register information

• Power management

• How to connect to external elements

• How to access external ROM

• FW download interface

• Battery charging function

Guidance Readers of this manual should already have a general knowledge of electronics,logic circuits, and microcomputers.

Notation This manual uses the following conventions:Data bit significance: High-order bits on the left side;

low-order bits on the right side Active low: XXXXB (Pin and signal names are suffixed with B.)

Note: Explanation of an indicated part of text

Caution: Information requiring the user’s special attention

Remark: Supplementary information

Numerical value: Binary ... xxxx or xxxxb

Decimal ... xxxx

Hexadecimal ... xxxxh

Related Document Use this manual in combination with the following document.

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

• μPD720201/μPD720202 Data Sheet: R19DS0047ECONTENTS

1. Overview..............................................................................................................................................1

1.1 Features....................................................................................................................................1

1.2 Applications.............................................................................................................................2

1.3 Ordering Information ..............................................................................................................2

1.4 Block Diagram .........................................................................................................................2

1.5 Pin Configuration (TOP VIEW) ...............................................................................................4

2. Pin Function........................................................................................................................................6

2.1 Power supply ...........................................................................................................................6

2.2 Analog Signal...........................................................................................................................6

2.3 System clock............................................................................................................................6

2.3.1 System Interface signal ...........................................................................................................7

2.3.2 PCI express Interface..............................................................................................................7

2.3.3 USB Interface..........................................................................................................................8

2.3.4 SPI Interface..........................................................................................................................10

3. Register Information ........................................................................................................................11

3.1 Register Attributes ................................................................................................................11

3.2 PCI Configuration Space ......................................................................................................12

3.2.1 PCI Type 0 Configuration Space Header ..............................................................................12

3.2.1.1 Vendor ID Register ..........................................................................................14

3.2.1.2 Device ID Register...........................................................................................14

3.2.1.3 Command Register..........................................................................................14

3.2.1.4 Status Register ................................................................................................15

3.2.1.5 Revision ID Register ........................................................................................16

3.2.1.6 Class Code Register ........................................................................................16

3.2.1.7 Cache Line Size Register ................................................................................16

3.2.1.8 Latency Timer Register....................................................................................17

3.2.1.9 Header Type Register......................................................................................17

3.2.1.10 BIST Register...................................................................................................17

3.2.1.11 Base Address Register #0 ...............................................................................17

3.2.1.12 Base Address Register #1 ...............................................................................18

3.2.1.13 Subsystem Vendor ID Register........................................................................18

3.2.1.14 Subsystem ID Register ....................................................................................18

3.2.1.15 Capabilities Pointer Register............................................................................18

3.2.1.16 Interrupt Line Register .....................................................................................19

3.2.1.17 Interrupt Pin Register .......................................................................................19

3.2.1.18 Min_Gnt Register.............................................................................................19

3.2.1.19 Max_LAT Register ...........................................................................................19

3.2.1.20 Serial Bus Release Number Register (SBRN) .................................................19

3.2.1.21 Frame Length Adjustment Register (FLADJ) ...................................................20

3.2.2 PCI Power Management Capabilities....................................................................................21

3.2.2.1 Capabilities List Register .................................................................................21

3.2.2.2 Power Management Capabilities Register (PMC)............................................21

3.2.2.3 Power Management Status / Control Register (PMSC) ...................................22

3.2.3 MSI Capabilities ....................................................................................................................24

3.2.3.1 Capabilities List Register for MSI.....................................................................24

3.2.3.2 Message Control for MSI .................................................................................24

3.2.3.3 Message Address for MSI................................................................................24

3.2.3.4 Message Upper Address for MSI.....................................................................24

3.2.3.5 Message Data for MSI .....................................................................................25

3.2.3.6 Mask Bits for MSI.............................................................................................25

3.2.3.7 Pending Bits for MSI ........................................................................................25

3.2.4 MSI-X Capabilities.................................................................................................................26

3.2.4.1 Capabilities List Register for MSI-X .................................................................26

3.2.4.2 Message Control for MSI-X..............................................................................26

3.2.4.3 Table Offset / Table BIR for MSI-X ..................................................................26

3.2.4.4 PBA Offset for MSI-X .......................................................................................27

3.2.5 PCI Express Extended Capabilities.......................................................................................28

3.2.5.1 PCI Express Capabilities List Register.............................................................28

3.2.5.2 PCI Express Capabilities Register ...................................................................28

3.2.5.3 Device Capabilities Register ............................................................................28

3.2.5.4 Device Control Register ...................................................................................29

3.2.5.5 Device Status Register ....................................................................................30

3.2.5.6 Link Capabilities Register ................................................................................31

3.2.5.7 Link Control Register .......................................................................................31

3.2.5.8 Link Status Register.........................................................................................33

3.2.5.9 Device Capabilities 2 Register .........................................................................33

3.2.5.10 Device Control 2 Register ................................................................................33

3.2.5.11 Device Status 2 Register .................................................................................34

3.2.5.12 Link Capabilities 2 Register .............................................................................34

3.2.5.13 Link Control 2 Register ....................................................................................34

3.2.5.14 Link Status 2 Register......................................................................................35

3.2.6 RENESAS Specific Registers................................................................................................36

3.2.6.1 FW Version Register........................................................................................36

3.2.6.2 PHY Control 0 Register....................................................................................36

3.2.6.3 PHY Control 1 Register....................................................................................36

3.2.6.4 PHY Control 2 Register....................................................................................36

3.2.6.5 Host Controller Configuration (HCConfiguration) Register...............................38

3.2.6.6 External ROM Information Register .................................................................40

3.2.6.7 External ROM Configuration Register..............................................................40

3.2.6.8 FW Download Control and Status Register .....................................................40

3.2.6.9 External ROM Access Control and Status Register.........................................41

3.2.6.10 DATA0 Register...............................................................................................42

3.2.6.11 DATA1 Register...............................................................................................43

3.2.7 Advanced Error Reporting Capabilities .................................................................................44

3.2.7.1 Advanced Error Reporting Enhanced Capability Header Register...................44

3.2.7.2 Uncorrectable Error Status Register ................................................................44

3.2.7.3 Uncorrectable Error Mask Register..................................................................45

3.2.7.4 Uncorrectable Error Severity Register .............................................................45

3.2.7.5 Correctable Error Status Register....................................................................46

3.2.7.6 Correctable Error Mask Register......................................................................46

3.2.7.7 Advanced Error Capabilities and Control Register...........................................47

3.2.7.8 Header Log Register........................................................................................47

3.2.8 Device Serial Number Enhanced Capability..........................................................................48

3.2.8.1 Device Serial Number Enhanced Capability Header Register .........................48

3.2.8.2 Serial Number Register....................................................................................48

3.2.9 Latency Tolerance Reporting (LTR) Capability......................................................................49

3.2.9.1 LTR Extended Capability Header Register ......................................................49

3.2.9.2 Max Snoop Latency Register...........................................................................49

3.2.9.3 Max No-Snoop Latency Register .....................................................................49

3.3 Host Controller Capability Register.....................................................................................50

3.3.1 Capability Registers Length (CAPLENGTH) .........................................................................50

3.3.2 Host Controller Interface Version Number (HCIVERSION) ...................................................50

3.3.3 Structural Parameters 1 (HCSPARAMS1) ............................................................................51

3.3.4 Structural Parameters 2 (HCSPARAMS2) ............................................................................51

3.3.5 Structural Parameters 3 (HCSPARAMS3) ............................................................................52

3.3.6 Capability Parameters (HCCPARAMS).................................................................................52

3.3.7 Doorbell Offset (DBOFF).......................................................................................................54

3.3.8 Runtime Register Space Offset (RTSOFF) ...........................................................................54

3.4 Host Controller Operational Registers................................................................................55

3.4.1 USB Command Register (USBCMD) ....................................................................................56

3.4.2 USB Status Register (USBSTS)............................................................................................58

3.4.3 Page Size Register (PAGESIZE) ..........................................................................................59

3.4.4 Device Notification Control Register (DNCTRL)....................................................................60

3.4.5 Command Ring Control Register (CRCR).............................................................................61

3.4.6 Device Context Base Address Array Pointer Register (DCBAAP).........................................63

3.4.7 Configure Register (CONFIG) ...............................................................................................63

3.4.8 Host Controller Port Register Set ..........................................................................................64

3.4.8.1 Port Status and Control Register (PORTSC) ...................................................65

3.4.8.2 Port PM Status and Control Register (PORTPMSC) .......................................70

3.4.8.3 USB3 Protocol PORTPMSC definition.............................................................71

3.4.8.4 USB2 Protocol PORTPMSC definition.............................................................72

3.4.8.5 Port Link Info Register (PORTLI) .....................................................................74

3.5 Host Controller Runtime Registers .....................................................................................75

3.5.1 Microframe Index Register (MFINDEX).................................................................................75

3.5.2 Interrupter Register Set .........................................................................................................76

3.5.2.1 Interrupter Management Register (IMAN)........................................................76

3.5.2.2 Interrupter Moderation Register (IMOD) ..........................................................77

3.5.2.3 Event Ring Segment Table Size Register (ERSTSZ) ......................................78

3.5.2.4 Event Ring Segment Table Base Address Register (ERSTBA).......................78

3.5.2.5 Event Ring Dequeue Pointer Register (ERDP)................................................79

3.6 Doorbell Registers.................................................................................................................80

3.7 xHCI Extended Capabilities..................................................................................................81

3.7.1 USB Legacy Support Capability ............................................................................................81

3.7.1.1 USB Legacy Support Capability (USBLEGSUP)..............................................81

3.7.1.2 USB Legacy Support Control / Status (USBLEGCTLSTS) ..............................82

3.7.2 xHCI Supported Protocol Capability......................................................................................84

3.7.2.1 USB 3.0 Supported Protocol Capability ...........................................................84

3.7.2.2 USB 2.0 Supported Protocol Capability ...........................................................85

3.7.3 Debug Capability...................................................................................................................87

3.7.3.1 Debug Capability ID Register...........................................................................87

3.7.3.2 Debug Capability Doorbell Register .................................................................88

3.7.3.3 Debug Capability Event Ring Segment Table Size Register............................88

3.7.3.4 Debug Capability Event Ring Segment Table Base Address Register ............88

3.7.3.5 Debug Capability Event Ring Dequeue Pointer Register .................................89

3.7.3.6 Debug Capability Event Ring Dequeue Pointer Register .................................89

3.7.3.7 Debug Capability Status Register ....................................................................91

3.7.3.8 Debug Capability Port Status and Control Register .........................................92

3.7.3.9 Debug Capability Context Pointer Register......................................................94

3.7.3.10 Debug Capability Device Descriptor Info Register 1 ........................................94

3.7.3.11 Debug Capability Device Descriptor Info Register 2 ........................................94

3.8 MSI-X / PBA Table..................................................................................................................96

3.8.1 Message Address for MSI-X Table........................................................................................96

3.8.2 Message Upper Address for MSI-X Table.............................................................................96

3.8.3 Message Data for MSI-X .......................................................................................................96

3.8.4 Vector Control for MSI-X .......................................................................................................97

3.8.5 Pending Bits for MSI-X PBA Entries......................................................................................97

4. Power Management..........................................................................................................................98

4.1 Power Management States...................................................................................................98

4.1.1 PCI Express Link State Power Management (L-States)........................................................98

4.1.2 PCI Express Device Power Management States (D-States) .................................................99

4.1.3 CLKREQ# Signal...................................................................................................................99

4.1.4 Summary of PCI Express Power Management States ........................................................100

4.2 Power Management Event (PME) Mechanism..................................................................101

4.2.1 PME support........................................................................................................................101

4.2.2 Pin configuration for supporting PME generation from D3cold............................................101

4.2.3 Timing Diagram for PME .....................................................................................................102

4.2.4 Wakeup Events ...................................................................................................................104

4.3 Control for System Clock Operation .................................................................................105

4.3.1 Clock system.......................................................................................................................105

5. How to Connect to External Elements .........................................................................................106

5.1 Handling Unused Pins ........................................................................................................106

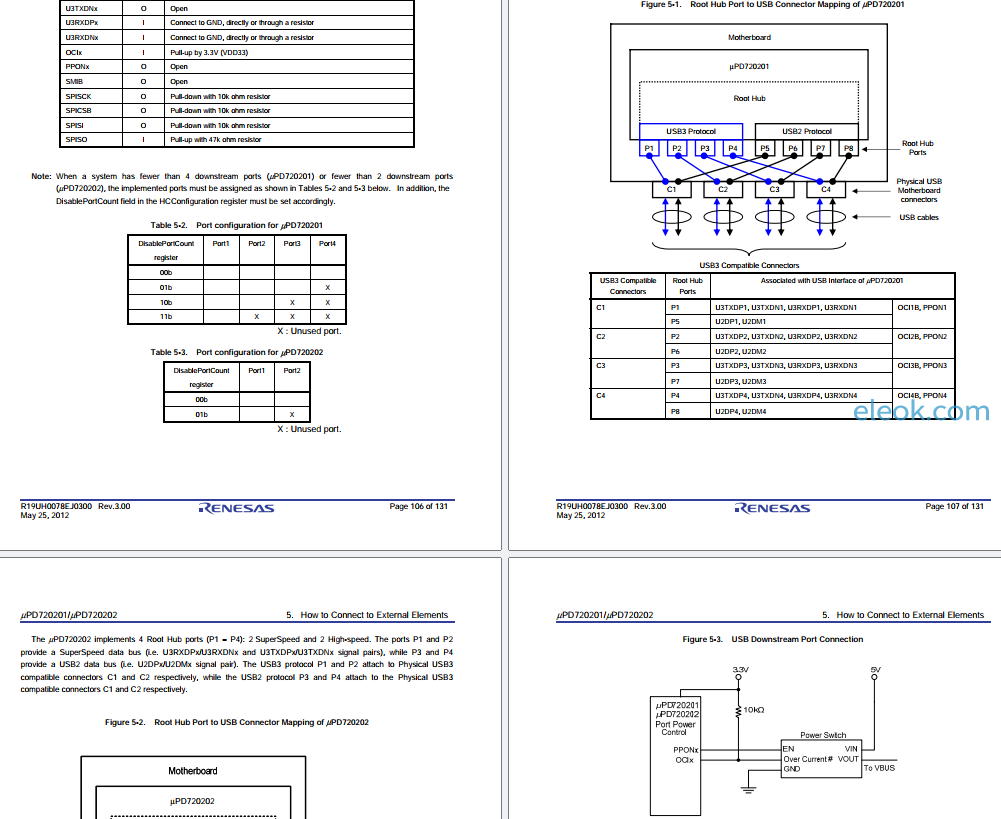

5.2 USB Port Connection..........................................................................................................107

5.3 Analog Circuit Connection .................................................................................................111

5.4 Crystal Connection..............................................................................................................112

5.5 External Serial ROM Connection .......................................................................................113

5.6 PCI Express Interface Connection.....................................................................................115

5.7 SMIB/SMI Interface Connection .........................................................................................116

6. How to Access External ROM .......................................................................................................117

6.1 Access External ROM Registers........................................................................................117

6.2 Access External ROM .........................................................................................................119

6.2.1 How to write FW to External ROM.......................................................................................119

6.2.1.1 Outline ...........................................................................................................119

6.2.1.2 Sequence to write the FW (External ROM data) of μPD720201 and

μPD720202 ...................................................................................................119

6.2.2 How to read ROM Data from External ROM........................................................................120

6.2.2.1 Outline ...........................................................................................................120

6.2.2.2 Sequence to read External ROM data from External ROM............................120

6.2.3 How to erase the data of the whole chip to be “1b” (Chip Erase) ........................................120

6.2.3.1 Outline ...........................................................................................................120

6.2.3.2 Sequence for Chip Erase...............................................................................120

6.3 Data Format..........................................................................................................................121

6.3.1 Firmware .............................................................................................................................121

6.3.2 Vendor Specific Configuration Data Block...........................................................................122

6.3.2.1 Data Format...................................................................................................122

6.3.2.2 Address map for Vendor Specific Configuration Block...................................122

6.3.2.3 External ROM Data........................................................................................1246.3.3 CRC16 calculation...............................................................................................................125

6.3.4 External ROM Data format ..................................................................................................126

6.3.4.1 First External ROM Image Data Block of Figure 6-4......................................126

6.3.4.2 Second External ROM Image Data Block of Figure 6-4.................................126

6.3.4.3 Loading the FW from the External ROM ........................................................126

7. FW Download Interface..................................................................................................................128

7.1 How to Download a Firmware into μPD720201/μPD720202............................................128

7.1.1 FW download registers........................................................................................................128

7.1.2 Outline of FW download sequences....................................................................................128

7.1.3 FW download sequences ....................................................................................................128

8. Battery Charging Function ............................................................................................................130

8.1 Features................................................................................................................................130

8.2 Battery Charging Mode.......................................................................................................130

8.3 How to Set Up ......................................................................................................................131

8.3.1 HW configuration requirement.............................................................................................131

4-1 Link Power Management State Flow Diagram ..............................................................................................98

4-2 Wake Up State Transition from D3cold (AUXDET bit = ‘1’).........................................................................102

4-3 Wake Up State Transition only from D3hot .................................................................................................103

4-4 μPD720201/202’s Clock System.................................................................................................................105

5-1 Root Hub Port to USB Connector Mapping of μPD720201 .........................................................................107

5-2 Root Hub Port to USB Connector Mapping of μPD720202 .........................................................................108

5-3 USB Downstream Port Connection .............................................................................................................109

5-4 Prohibited USB Downstream Port Connection............................................................................................110

5-5 RREF Connection .......................................................................................................................................111

5-6 Crystal Connection......................................................................................................................................112

5-7 External Serial ROM Connection ................................................................................................................113

5-8 Unused Pins Connection When the External Serial ROM Is Not Mounted..................................................114

5-9 PCI Express Interface Connection ..............................................................................................................115

5-10 SMIB Interface Connection .......................................................................................................................116

6-1 Firmware .....................................................................................................................................................121

6-2 Vendor Specific Configuration Data Block ..................................................................................................122

6-3 External ROM Data .....................................................................................................................................124

6-4 External ROM Data Format.........................................................................................................................126

8-1 VBUS Control Configuration with Battery Charging Function......................................................................131

3-1 Register and Register Bit-Field Types...........................................................................................................11

3-2 PCI Type 0 Configuration Space Header ......................................................................................................12

3-3 Vendor ID Register (Offset Address: 00h).....................................................................................................14

3-4 Device ID Register (Offset Address: 02h) .....................................................................................................14

3-5 Command Register (Offset Address: 04h) ....................................................................................................14

3-6 Status Register (Offset Address: 06h)...........................................................................................................15

3-7 Revision ID Register (Offset Address: 08h) ..................................................................................................16

3-8 Class Code Register (Offset Address: 09h) ..................................................................................................16

3-9 Cache Line Size Register (Offset Address: 0Ch) ..........................................................................................16

3-10 Latency Timer Register (Offset Address: 0Dh)............................................................................................17

3-11 Header Type Register (Offset Address: 0Eh)..............................................................................................17

3-12 BIST Register (Offset Address: 0Fh)...........................................................................................................17

3-13 Base Address Register #0 (Offset Address: 10h)........................................................................................17

3-14 Base Address Register #1 (Offset Address: 14h)........................................................................................18

3-15 Subsystem Vendor ID Register (Offset Address: 2Ch) ...............................................................................18

3-16 Subsystem ID Register (Offset Address: 2Eh) ............................................................................................18

3-17 Capabilities Pointer Register (Offset Address: 34h) ....................................................................................18

3-18 Interrupt Line Register (Offset Address: 3Ch) .............................................................................................19

3-19 Interrupt Pin Register (Offset Address: 3Dh)...............................................................................................19

3-20 Min_Gnt Register (Offset Address: 3Eh).....................................................................................................19

3-21 Max_Lat Register (Offset Address: 3Fh).....................................................................................................19

3-22 SBRN Register (Offset Address: 60h).........................................................................................................19

3-23 FLADJ Register (Offset Address: 61h)........................................................................................................20

3-24 Capabilities List Register (Offset Address: 50h)..........................................................................................21

3-25 PMC Register (Offset Address: 52h)...........................................................................................................21

3-26 PMSC Register (Offset Address: 54h) ........................................................................................................22

3-27 Capabilities List Register (Offset Address: 70h)..........................................................................................24

3-28 Message Control Register (Offset Address: 72h)........................................................................................24

3-29 Message Address Register (Offset Address: 74h) ......................................................................................24

3-30 Message Upper Address Register (Offset Address: 78h) ...........................................................................24

3-31 Message Data Register (Offset Address: 7Ch) ...........................................................................................25

3-32 Mask Bits Register (Offset Address: 80h) ...................................................................................................25

3-33 Pending Bits Register (Offset Address: 84h)...............................................................................................25

3-34 Capabilities List Register (Offset Address: 90h)..........................................................................................26

3-35 Message Control Register (Offset Address: 92h)........................................................................................26

3-36 Table Offset / Table BIR Register (Offset Address: 94h) ............................................................................26

3-37 Message Upper Address Register (Offset Address: 98h) ...........................................................................27

3-38 PCI Express Capabilities List Register (Offset Address: A0h).....................................................................28

3-39 PCI Express Capabilities Capability Register (Offset Address: A2h) ..........................................................28

3-40 Device Capabilities Register (Offset Address: A4h) ....................................................................................28

3-41 Device Control Register (Offset Address: A8h)...........................................................................................29

3-42 Device Status Register (Offset Address: AAh)............................................................................................30

3-43 Link Capabilities Register (Offset Address: ACh)........................................................................................31

3-44 Link Control Register (Offset Address: B0h) ...............................................................................................31

3-45 Link Status Register (Offset Address: B2h).................................................................................................33

3-46 Device Capabilities 2 Register (Offset Address: C4h).................................................................................33

3-47 Device Control 2 Register (Offset Address: C8h)........................................................................................33

3-48 Device Status 2 Register (Offset Address: CAh).........................................................................................34

3-49 Link Capabilities 2 Register (Offset Address: CCh).....................................................................................34

3-50 Link Control 2 Register (Offset Address: D0h) ............................................................................................34

3-51 Link Status 2 Register (Offset Address: D2h)..............................................................................................35

3-52 FW Register (Offset Address: 6Ch).............................................................................................................36

3-53 PHY Control 0 Register (Offset Address: DCh)...........................................................................................36

3-54 PHY Control 1 Register (Offset Address: E0h)............................................................................................36

3-55 PHY Control 2 Register (Offset Address: E4h)............................................................................................36

3-56 HCConfiguration Register (Offset Address: E8h)........................................................................................38

3-57 External ROM Information Register (Offset Address: ECh).........................................................................40

3-58 External ROM Configuration Register (Offset Address: F0h)......................................................................40

3-59 FW Download Control and Status Register (Offset Address: F4h)..............................................................40

3-60 FW Control and Status Register (Offset Address: F6h) ..............................................................................41

3-61 DATA0 Register (Offset Address: F8h) .......................................................................................................42

3-62 DATA1 Register (Offset Address: FCh) ......................................................................................................43

3-63 Advanced Error Reporting Enhanced Capability Header Register (Offset Address: 100h) .........................44

3-64 Uncorrectable Error Status Register (Offset Address: 104h).......................................................................44

3-65 Uncorrectable Error Status Register (Offset Address: 108h).......................................................................45

3-66 Uncorrectable Error Severity Register (Offset Address: 10Ch) ...................................................................45

3-67 Correctable Error Status Register (Offset Address: 110h) ..........................................................................46

3-68 Correctable Error Mask Register (Offset Address: 114h)............................................................................46

3-69 Advanced Error Capabilities and Control Register (Offset Address: 118h) .................................................47

3-70 Header Log Register (Offset Address: 11Ch)..............................................................................................47

3-71 Device Serial Number Enhanced Capability Header Register (Offset Address: 140h)................................48

3-72 Serial Number Register (Offset Address: 144h)..........................................................................................48

3-73 LTR Extended Capability Header Register (Offset Address: 150h).............................................................49

3-74 Max Snoop Latency Register (Offset Address: 154h) .................................................................................49

3-75 Max No-Snoop Latency Register (Offset Address: 156h) ...........................................................................49

3-76 eXtensible Host Controller Capability..........................................................................................................50

3-77 CAPLENGTH (Offset Address: Base + 00h)...............................................................................................50

3-78 HCIVERSION (Offset Address: Base + 02h)...............................................................................................50

3-79 HCSPARAMS1 (Offset Address: Base + 04h) ............................................................................................51

3-80 HCSPARAMS2 (Offset Address: Base + 08h) ............................................................................................51

3-81 HCSPARAMS3 (Offset Address: Base + 0Ch)............................................................................................52

3-82 HCCPARAMS (Offset Address: Base + 10h) ..............................................................................................52

3-83 DBOFF (Offset Address: Base + 14h).........................................................................................................54

3-84 RTSOFF Offset (Offset Address: Base + 18h) ............................................................................................54

3-85 Host Controller Operational Registers.........................................................................................................55

3-86 USBCMD Register (Offset Address: Operational Base (20h) + 00h) ..........................................................56

3-87 USBSTS Register (Offset Address: Operational Base (20h) + 04h)............................................................58

3-88 PAGESIZE Register (Offset Address: Operational Base (20h) + 08h)........................................................59

3-89 DNCTRL Register (Offset Address: Operational Base (20h) + 14h) ...........................................................60

3-90 CRCR Register (Offset Address: Operational Base (20h) + 18h) ...............................................................61

3-91 DCBAAP Register (Offset Address: Operational Base (20h) + 30h) ...........................................................63

3-92 CONFIG Register (Offset Address: Operational Base (20h) + 38h)............................................................63

3-93 Host Controller Port Register Set (Offset shows from Base).......................................................................64

3-94 PORTSC Register (Offset Address: Operational Base (20h) + (400h + (10h *(n-1))) .................................65

3-95 PLS Write Value..........................................................................................................................................69

3-96 PLS Read Value..........................................................................................................................................70

3-97 PLS transitions ............................................................................................................................................70

3-98 USB3 PORTPMSC Register (Offset Address: Operational Base (20h) + (404h + (10h*(n-1)))...................71

3-99 USB2 PORTPMSC Register (Offset Address: Operational Base (20h) +(404h + (10h*(n-1)))....................72

3-100 USB3 PORTLI Register (Offset Address: Operational Base (20h) + (408h + (10h * (n-1))) ......................74

3-101 Host Controller Runtime Registers............................................................................................................75

3-102 MFINDEX Register (Offset Address: Runtime Base (600h) + 00h)...........................................................75

3-103 Interrupter Register Set.............................................................................................................................76

3-104 IMAN Register (Offset Address: Runtime Base (600h) + 020h + (20h*Interrupter))..................................76

3-105 IMOD Register (Offset Address: Runtime Base (600h) + 024h + (20h*Interrupter)) .................................77

3-106 ERSTSZ Register (Offset Address: Runtime Base (600h) + 028h + (20h*Interrupter)).............................78

3-107 ERSTBA Register (Offset Address: Runtime Base (600h) + 30h + (20h*Interrupter)) ..............................78

3-108 ERDP Register (Offset Address: Runtime Base (600h) + 038h + (20h*Interrupter)).................................79

3-109 Doorbell Registers.....................................................................................................................................80

3-110 Doorbell Register ......................................................................................................................................80

3-111 HC Extended Capability Registers ............................................................................................................81

3-112 USBLEGSUP (Offset Address: xECP (500h) + 00h).................................................................................81

3-113 USBLEGCTLSTS (Offset Address: xECP (500h) + 04h) ..........................................................................82

3-114 xHCI Supported Protocol Capability Register............................................................................................84

3-115 Offset 00h - xHCI Supported Protocol Capability Field (Offset Address: xECP + 10h (510h))..................84

3-116 Offset 04h - xHCI Supported Protocol Capability Field (Offset Address: xECP + 14h (514h))..................84

3-117 Offset 08h - xHCI Supported Protocol Capability Field (Offset Address: xECP + 18h (518h))..................84

3-118 Offset 0Ch - xHCI Supported Protocol Capability Field (Offset Address: xECP + 1Ch (51Ch)) ................85

3-119 Offset 00h - xHCI Supported Protocol Capability Field (Offset Address: xECP + 24h (524h))..................85

3-120 Offset 04h - xHCI Supported Protocol Capability Field (Offset Address: xECP + 28h (528h))..................85

3-121 Offset 08h - xHCI Supported Protocol Capability Field (Offset Address: xECP + 2Ch (52Ch)).................86

3-122 Offset 0Ch - xHCI Supported Protocol Capability Field (Offset Address: xECP + 30h (530h)) .................86

3-123 Debug Capability Register Layout.............................................................................................................87

3-124 Offset 00h – Debug Capability Field (Offset Address: xECP + 50h (550h)) ..............................................87

3-125 Offset 04h – Debug Capability Field (Offset Address: xECP + 54h (554h)) ..............................................88

3-126 Offset 08h – Debug Capability Field (Offset Address: xECP + 58h (558h)) ..............................................88

3-127 Offset 0Ch – Debug Capability Field (Offset Address: xECP + 60h (560h))..............................................88

3-128 Offset 18h – Debug Capability Field (Offset Address: xECP + 68h (568h)) ..............................................89

3-129 Offset 20h – Debug Capability Field (Offset Address: xECP + 70h (570h)) ..............................................89

3-130 Offset 24h – Debug Capability Field (Offset Address: xECP + 74h (574h)) ..............................................91

3-131 Offset 28h – Debug Capability Field (Offset Address: xECP + 78h (578h)) ..............................................92

3-132 Offset 30h – Debug Capability Field (Offset Address: xECP + 80h (580h)) ..............................................94

3-133 Offset 38h – Debug Capability Field (Offset Address: xECP + 88h (588h)) ..............................................94

3-134 Offset 3Ch – Debug Capability Field (Offset Address: xECP + 8Ch (58Ch)) ............................................94

3-135 MSI-X Table Registers ..............................................................................................................................96

3-136 PBA Table Registers.................................................................................................................................96

3-137 Message Address (Offset Address: Base + 1000h + (10h*Interrupter)) ....................................................96

3-138 Message Upper Address (Offset Address: Base + 1004h + (10h*Interrupter)) .........................................96

3-139 Message Data (Offset Address: Base + 1008h + (10h*Interrupter))..........................................................96

3-140 Message Data (Offset Address: Base + 100Ch + (10h*Interrupter)) .........................................................97

3-141 Message Data (Offset Address: Base + 1080h)........................................................................................97

4-1 PCI Express Link States ...............................................................................................................................98

4-2 PCI Express Device Power Management States ..........................................................................................99

4-3 Operation of CLKREQ# Signal......................................................................................................................99

4-4 Summary of PCI Express Power Management States................................................................................100

4-5 Wakeup Events...........................................................................................................................................104

5-1 Unused Pin Connection ..............................................................................................................................106

5-2 Port configuration for μPD720201...............................................................................................................106

5-3 Port configuration for μPD720202...............................................................................................................106

5-4 Supported External Serial ROM List ...........................................................................................................113

6-1 External ROM Information & Parameter......................................................................................................118

6-2 Firmware Block Description.........................................................................................................................121

6-3 Vendor Specific Configuration Data Block Description................................................................................122

6-4 Address Map for Vendor Specific Configuration Block................................................................................122

8-1 Battery Charging Mode ...............................................................................................................................130

部分内容截图

【必读】版权免责声明

1、本主题所有言论和内容纯属会员个人意见,与本论坛立场无关。2、本站对所发内容真实性、客观性、可用性不做任何保证也不负任何责任,网友之间仅出于学习目的进行交流。3、对提供的数字内容不拥有任何权利,其版权归原著者拥有。请勿将该数字内容进行商业交易、转载等行为,该内容只为学习所提供,使用后发生的一切问题与本站无关。 4、本网站不保证本站提供的下载资源的准确性、安全性和完整性;同时本网站也不承担用户因使用这些下载资源对自己和他人造成任何形式的损失或伤害。 5、本网站所有软件和资料均为网友推荐收集整理而来,仅供学习用途使用,请务必下载后两小时内删除,禁止商用。6、如有侵犯你版权的,请及时联系我们(电子邮箱1370723259@qq.com)指出,本站将立即改正。

|